去年(大一下)的時候,因緣際會下加入了班上同學創的小小讀書會。原本一開始聚會方向大致在分享自己高中時代學習的心路歷程,後來系主任告訴我們學校有鼓勵學生進行自主學習計畫的比賽。報名後才開始找到了讀書會的新目標:

製作一個二進制鐘

於是我們預習了邏輯設計課程後面的循序邏輯章節,學習了正反器的使用和計數器的組成。

在電路模擬上,由於當時尚未接觸到一些進階的電路模擬軟體與硬體描述語言,所以依照我一貫的摸索模式:

搜尋 Opensource+Logic+Simulator就很幸運的找到了 CEDAR Logic Simulator 這個方便的程式,就拿它來當我們主要的電路模擬和繪圖工具。

在硬體設計的時候遇到了一個比較大問題,就是要用何種方式呈現出我們所設計的邏輯電路?網路上大多是直接使用一顆單晶片來控制所有電路,但是為了要與所學習的課程契合,我們必須使用離散元件的方式來呈現。排除掉了複雜的電晶體邏輯,我們選擇使用 74XX 系列的積體電路。避免直接使用 7469 這類現成二進制計數器做出來過於簡化 ( 不夠刺激XD ) ,最後折衷用 7474 這個雙 D 型正反器來組合我們所有的計數器電路。

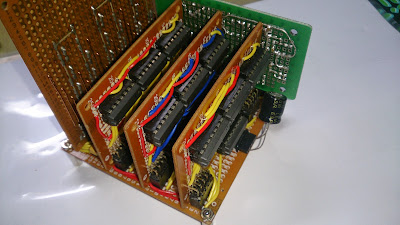

大概算了一下,驅動 60 秒和 60 分的電路各需要用到四顆 7474 來完成, 24 小時的部分因為十位較少,所以三顆 7474 就能解決。剛好可以把這 11 顆 7474 安排在三塊 25×15 孔的洞洞板上,底座製作一個連接底板來連接,把進位訊號先經過第四塊"手動設定/時脈產生"的板子,再與下一個模組連接。於是整個時鐘的雛形就大概成形了

|

| 74LS74 - dual D positive edge triggered flip-flop with preset and clear |

時脈產生的部分:原構想是想使用555來產生所需的 1Hz 方波,後來發現555使用的 RC 電路除了作為時鐘訊號原精度極低之外,原先使用555做出的"手動設定與時脈產生板"接線上有 BUG 無法正確顯示,直到最近重新設計使用 4060 除頻器搭配 32768KHz 石英諧震器和半顆 7474 (2Hz除至1Hz) 做一遍才成功。

|  |  |

| 手動設定與時脈產生板 Ver.1 | 手動設定與時脈產生板 Ver.2 (正面)Crystal再左下電阻旁 | 手動設定與時脈產生板 Ver.2 (反面)被動元件皆使用 SMT |

其他資料:

輔仁大學電機工成學系?

回覆刪除

刪除阿哈這段自介都用這麼久了自己都沒發現XD

已修正,感謝囉